## Summary

Atmel's SAM4L series is a member of a family of Flash microcontrollers based on the high performance 32-bit ARM Cortex-M4 RISC processor running at frequencies up to 48MHz.

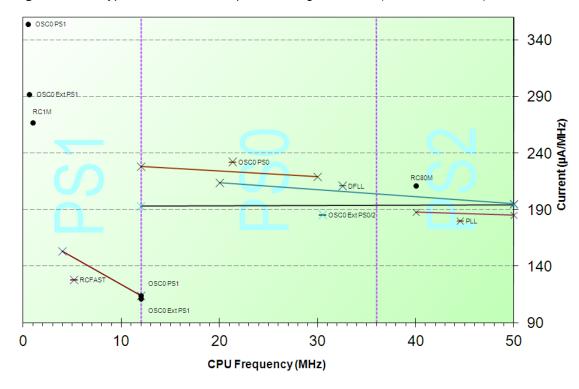

The SAM4L series embeds state-of-the-art picoPower technology for ultra-low power consumption. Combined power control techniques are used to bring active current consumption down to 90 $\mu$ A/MHz. The device allows a wide range of options between functionality and power consumption, giving the user the ability to reach the lowest possible power consumption with the feature set required for the application. The WAIT and RETENTION modes provide full logic and RAM retention, associated with fast wake-up capability (<1.5 $\mu$ s) and a very low consumption of, respectively, 3  $\mu$ A and 1.5  $\mu$ A. In addition, WAIT mode supports SleepWalking features. In BACKUP mode, CPU, peripherals and RAM are powered off and, while consuming less than 0.5 $\mu$ A with external interrupt wake-up supported.

The SAM4L series offers a wide range of peripherals such as segment LCD controller, embedded hardware capacitive touch (QTouch), USB device & embedded host, 128-bit AES and audio interfaces in addition to high speed serial peripherals such as USART, SPI and I<sup>2</sup>C. Additionally the Peripheral Event System and SleepWalking allows the peripherals to communicate directly with each other and make intelligent decisions and decide to wake-up the system on a qualified events on a peripheral level; such as I<sup>2</sup>C address match or and ADC threshold.

## Features

- Core

- ARM<sup>®</sup> Cortex<sup>™</sup>-M4 running at up to 48MHz

- Memory Protection Unit (MPU)

- Thumb<sup>®</sup>-2 instruction set

- picoPower<sup>®</sup> Technology for Ultra-low Power Consumption

- Active mode downto 90µA/MHz with configurable voltage scaling

- High performance and efficiency: 28 coremark/mA

- Wait mode downto 3µA with fast wake-up time (<1.5µs) supporting SleepWalking

- Full RAM and Logic Retention mode downto 1.5µA with fast wake-up time (<1.5µs)

- Ultra low power Backup mode with/without RTC downto 0.9/0.5µA

- Memories

- From 128 to 256 Kbytes embedded Flash, 64-bit wide access,

- 0 wait-state capability up to 24MHz

- up to 32Kbytes embedded SRAM

- System Functions

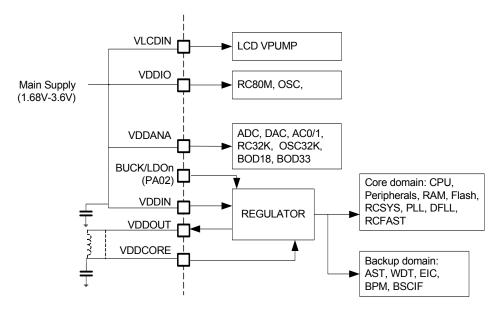

- Embedded voltage linear and switching regulator for single supply operation

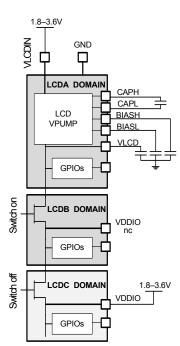

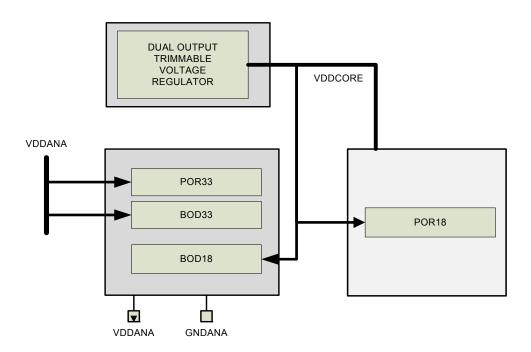

- Two Power-on-Reset and Two Brown-out Detectors (BOD)

- Quartz or ceramic resonator oscillators: 0.6 to 30MHz main power with Failure Detection and low power 32.768 kHz for RTC or device clock

- High precision 4/8/12MHz factory trimmed internal RC oscillator

- Slow Clock Internal RC oscillator as permanent low-power mode device clock

- High speed 80MHz internal RC oscillator

- Low power 32kHz internal RC oscillator

- PLL up to 240MHz for device clock and for USB

# Atmel

# ATSAM ARM-based Flash MCU

# **SAM4L Series**

## Summary

42023DS-03/2013

- Digital Frequency Locked Loop (DFLL) with wide input range

- Up to 16 peripheral DMA (PDCA) channels

- Peripherals

- USB 2.0 Device and Embedded Host: 12 Mbps, up to 8 bidirectional Endpoints and Multi-packet Ping-pong Mode. On-Chip Transceiver

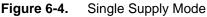

- Liquid Crystal Display (LCD) Module with Capacity up to 40 Segments and up to 4 Common Terminals

- One USART with ISO7816, IrDA®, RS-485, SPI, Manchester and LIN Mode

- Three USART with SPI Mode

- One PicoUART for extended UART wake-up capabilities in all sleep modes

- Windowed Watchdog Timer (WDT)

- Asynchronous Timer (AST) with Real-time Clock Capability, Counter or Calendar Mode Supported

- Frequency Meter (FREQM) for Accurate Measuring of Clock Frequency

- Six 16-bit Timer/Counter (TC) Channels with capture, waveform, compare and PWM mode

- One Master/Slave Serial Peripheral Interface (SPI) with Chip Select Signals

- Four Master and Two Slave Two-wire Interfaces (TWI), up to 3.4Mbit/s I<sup>2</sup>C-compatible

- One Advanced Encryption System (AES) with 128-bit key length

- One 16-channel ADC 300Ksps (ADC) with up to 12 Bits Resolution

- One DAC 500Ksps (DACC) with up to 10 Bits Resolution

- Four Analog Comparators (ACIFC) with Optional Window Detection

- Capacitive Touch Module (CATB) supporting up to 32 buttons

- Audio Bitstream DAC (ABDACB) Suitable for Stereo Audio

- Inter-IC Sound (IISC) Controller, Compliant with Inter-IC Sound (I<sup>2</sup>S) Specification

- Peripheral Event System for Direct Peripheral to Peripheral Communication

- 32-bit Cyclic Redundancy Check Calculation Unit (CRCCU)

- Random generator (TRNG)

- Parallel Capture Module (PARC)

- Glue Logic Controller (GLOC)

- I/O

- Up to 75 I/O lines with external interrupt capability (edge or level sensitivity), debouncing, glitch filtering and slew-rate control

Atmel

- Up to Six High-drive I/O Pins

- Single 1.68-3.6V Power Supply

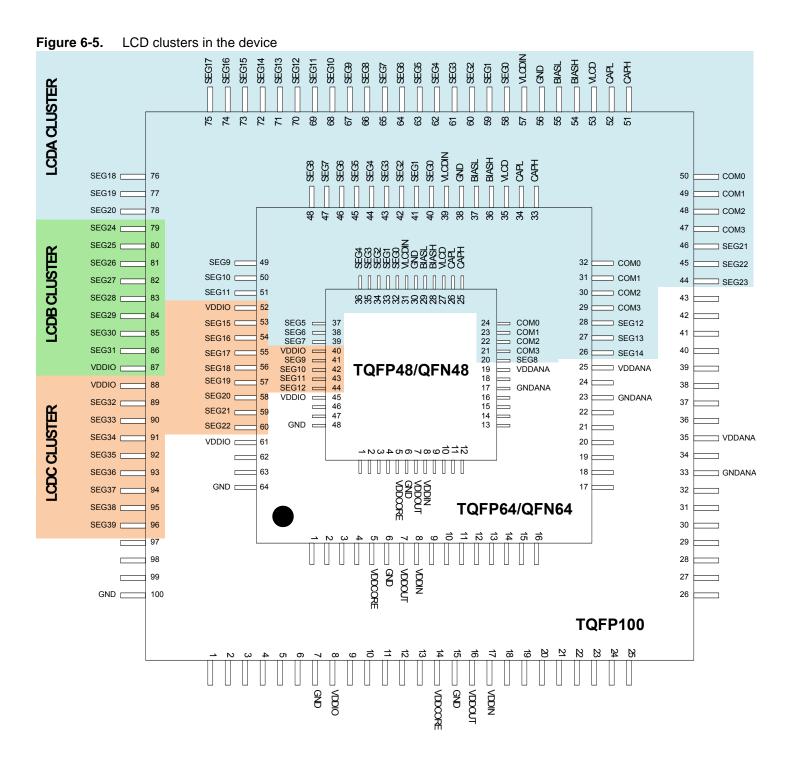

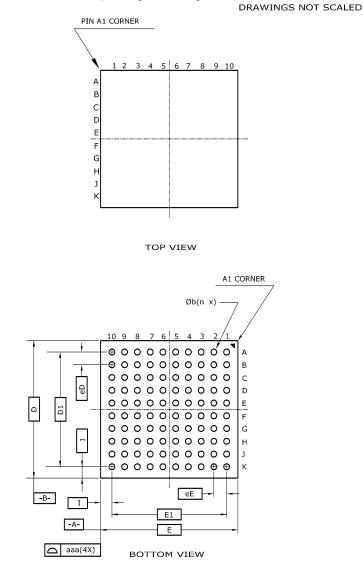

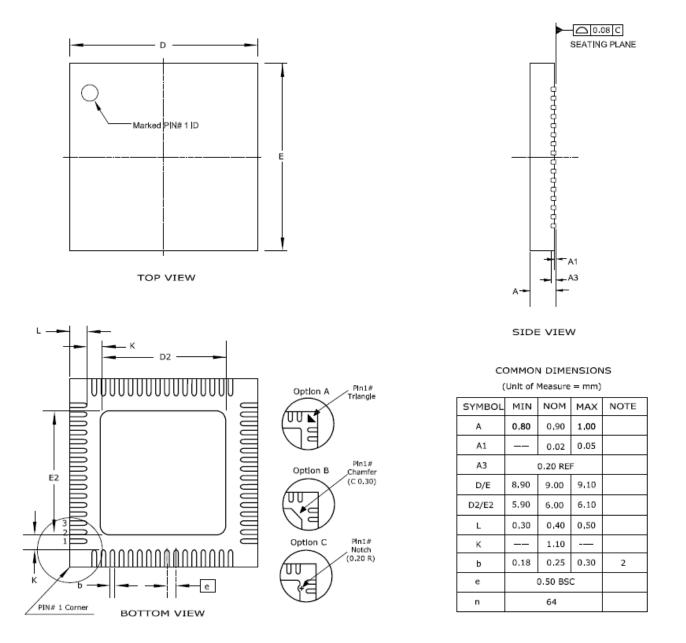

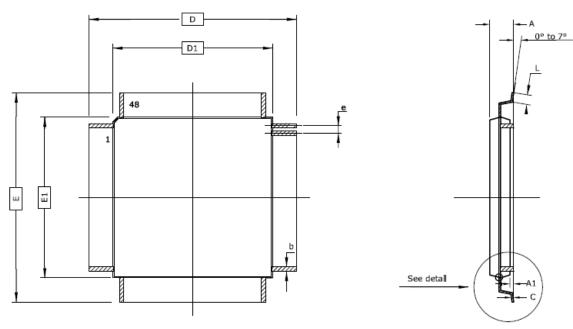

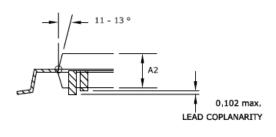

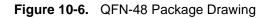

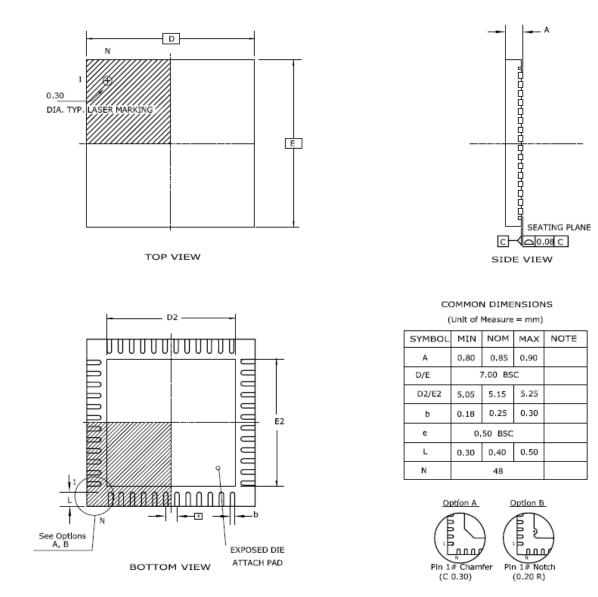

- Packages

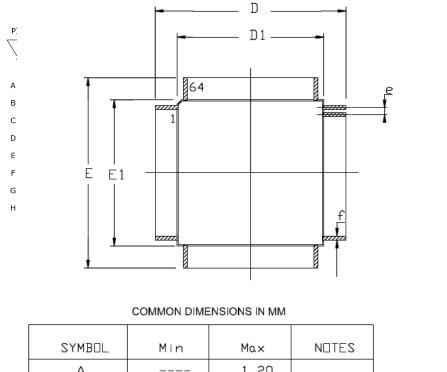

- 100-lead LQFP, 14 x 14 mm, pitch 0.5 mm/100-ball VFBGA, 7x7 mm, pitch 0.65 mm

- 64-lead LQFP, 10 x 10 mm, pitch 0.5 mm/64-pad QFN 9x9 mm, pitch 0.5 mm

- 48-lead LQFP, 7 x 7 mm, pitch 0.5 mm/48-pad QFN 7x7 mm, pitch 0.5 mm

## 1. Description

Atmel's SAM4L series is a member of a family of Flash microcontrollers based on the high performance 32-bit ARM Cortex-M4 RISC processor running at frequencies up to 48MHz.

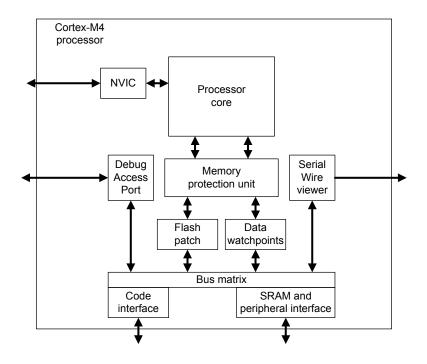

The processor implements a Memory Protection Unit (MPU) and a fast and flexible interrupt controller for supporting modern and real-time operating systems.

The ATSAM4L4/L2 embeds state-of-the-art picoPower technology for ultra-low power consumption. Combined power control techniques are used to bring active current consumption down to  $90\mu$ A/MHz. The device allows a wide range of options between functionality and power consumption, giving the user the ability to reach the lowest possible power consumption with the feature set required for the application. On-chip regulator improves power efficiency when used in swichting mode with an external inductor or can be used in linear mode if application is noise sensitive.

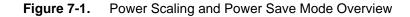

The ATSAM4L4/L2 supports 4 power saving strategies. The SLEEP mode put the CPU in idle mode and offers different sub-modes which automatically switch off/on bus clocks, PLL, oscillators. The WAIT and RETENTION modes provide full logic and RAM retention, associated with fast wake-up capability (<1.5 $\mu$ s) and a very low consumption of, respectively, 3  $\mu$ A and 1.5  $\mu$ A. In addition, WAIT mode supports SleepWalking features. In BACKUP mode, CPU, peripherals and RAM are powered off and, while consuming less than 0.5 $\mu$ A, the device is able to wake-up from external interrupts.

The ATSAM4L4/L2 incorporates on-chip Flash tightly coupled to a low power cache (LPCACHE) for active consumption optimization and SRAM memories for fast access.

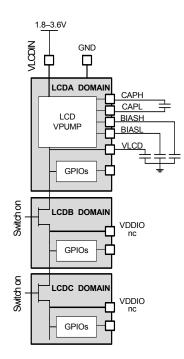

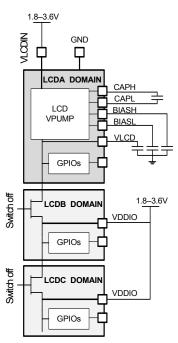

The LCD controller is intended for monochrome passive liquid crystal display (LCD) with up to 4 Common terminals and up to 40 Segments terminals. Dedicated Low Power Waveform, Contrast Control, Extended Interrupt Mode, Selectable Frame Frequency and Blink functionality are supported to offload the CPU, reduce interrupts and reduce power consumption. The LCD includes integrated LCD buffers, an integrated power supply voltage and an innovative SWAP mode. Using SWAP mode, the hardware designers have more flexibility during board layout as they can rearrange the pin sequence on Segment and/or Common Terminal Buses.

The low-power and high performance capacitive touch module (CATB) is introduced to meet the demand for a low power capacitive touch solution that could be used to handle buttons, sliders and wheels. The CATB provides excellent signal performance, as well as autonomous touch and proximity detection for up to 32 sensors. This solution includes an advanced sequencer in addition to an hardware filtering unit.

The Advanced Encryption Standard module (AESA) is compliant with the *FIPS (Federal Information Processing Standard) Publication 197, Advanced Encryption Standard (AES)*, which specifies a symmetric block cipher that is used to encrypt and decrypt electronic data. *Encryption* is the transformation of a usable message, called the *plaintext*, into an unreadable form, called the *ciphertext*. On the other hand, *decryption* is the transformation that recovers the plaintext from the ciphertext. AESA supports 128 bits cryptographic key sizes.

The Peripheral Direct Memory Access (DMA) controller enables data transfers between peripherals and memories without processor involvement. The Peripheral DMA controller drastically reduces processing overhead when transferring continuous and large data streams.

The Peripheral Event System (PES) allows peripherals to receive, react to, and send peripheral events without CPU intervention. Asynchronous interrupts allow advanced peripheral operation in low power modes.

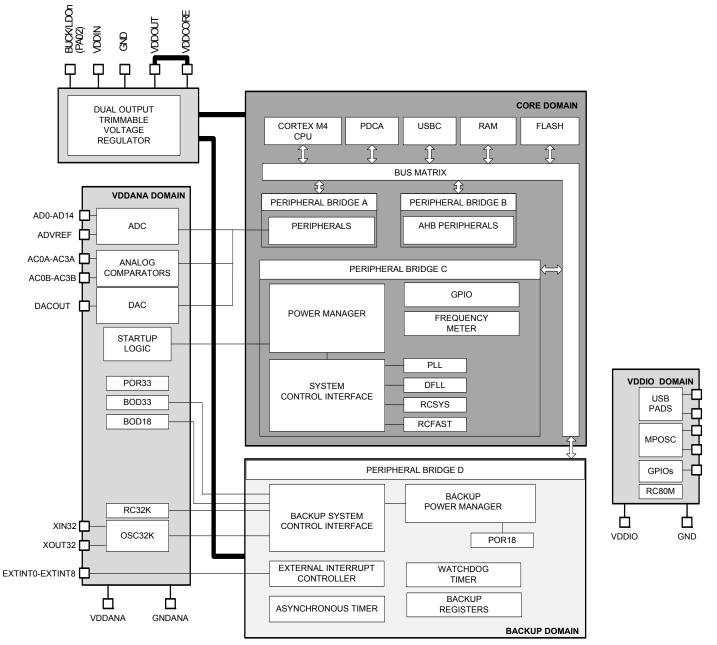

The Power Manager (PM) improves design flexibility and security. The Power Manager supports SleepWalking functionality, by which a module can be selectively activated based on peripheral events, even in sleep modes where the module clock is stopped. Power monitoring is supported by on-chip Power-on Reset (POR18, POR33), Brown-out Detectors (BOD18, BOD33). The device features several oscillators, such as Phase Locked Loop (PLL), Digital Frequency Locked Loop (DFLL), Oscillator 0 (OSC0), Internal RC 4,8,12MHz oscillator (RCFAST), system RC oscillator (RCSYS), Internal RC 80MHz, Internal 32kHz RC and 32kHz Crystal Oscillator. Either of these oscillators can be used as source for the system clock. The DFLL is a programmable internal oscillator from 40 to 150MHz. It can be tuned to a high accuracy if an accurate reference clock is running, e.g. the 32kHz crystal oscillator.

The Watchdog Timer (WDT) will reset the device unless it is periodically serviced by the software. This allows the device to recover from a condition that has caused the system to be unstable.

The Asynchronous Timer (AST) combined with the 32kHz crystal oscillator supports powerful real-time clock capabilities, with a maximum timeout of up to 136 years. The AST can operate in counter or calendar mode.

The Frequency Meter (FREQM) allows accurate measuring of a clock frequency by comparing it to a known reference clock.

The Full-speed USB 2.0 device and embedded host interface (USBC) supports several USB classes at the same time utilizing the rich end-point configuration.

The device includes six identical 16-bit Timer/Counter (TC) channels. Each channel can be independently programmed to perform frequency measurement, event counting, interval measurement, pulse generation, delay timing, and pulse width modulation.

The ATSAM4L4/L2 also features many communication interfaces, like USART, SPI, or TWI, for communication intensive applications. The USART supports different communication modes, like SPI Mode and LIN Mode.

A general purpose 16-channel ADC is provided, as well as four analog comparators (ACIFC). The ADC can operate in 12-bit mode at full speed. The analog comparators can be paired to detect when the sensing voltage is within or outside the defined reference window.

Atmel offers the QTouch Library for embedding capacitive touch buttons, sliders, and wheels functionality. The patented charge-transfer signal acquisition offers robust sensing and includes fully debounced reporting of touch keys as well as Adjacent Key Suppression<sup>®</sup> (AKS<sup>®</sup>) technology for unambiguous detection of key events. The easy-to-use QTouch Suite toolchain allows you to explore, develop, and debug your own touch applications.

The Audio Bitstream DAC (ABDACB) converts a 16-bit sample value to a digital bitstream with an average value proportional to the sample value. Two channels are supported, making the ABDAC particularly suitable for stereo audio.

The Inter-IC Sound Controller (IISC) provides a 5-bit wide, bidirectional, synchronous, digital audio link with external audio devices. The controller is compliant with the Inter-IC Sound (I2S) bus specification.

Atmel

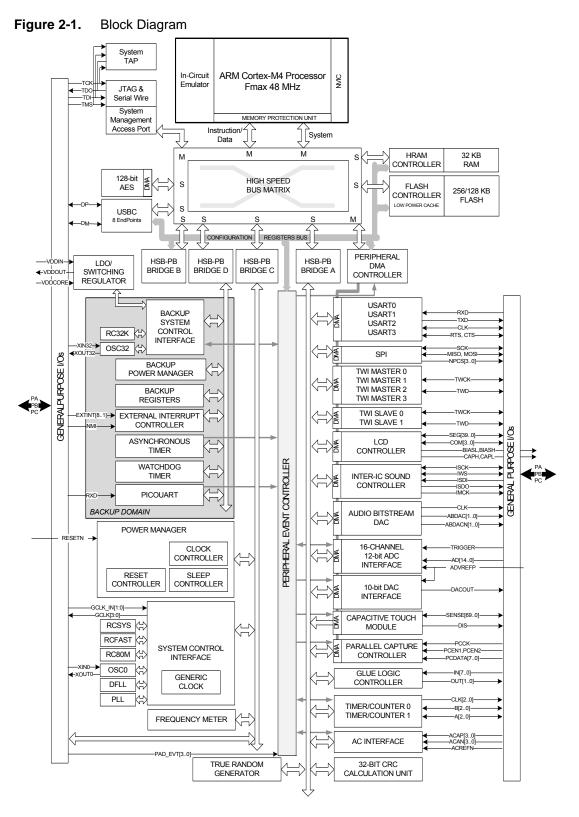

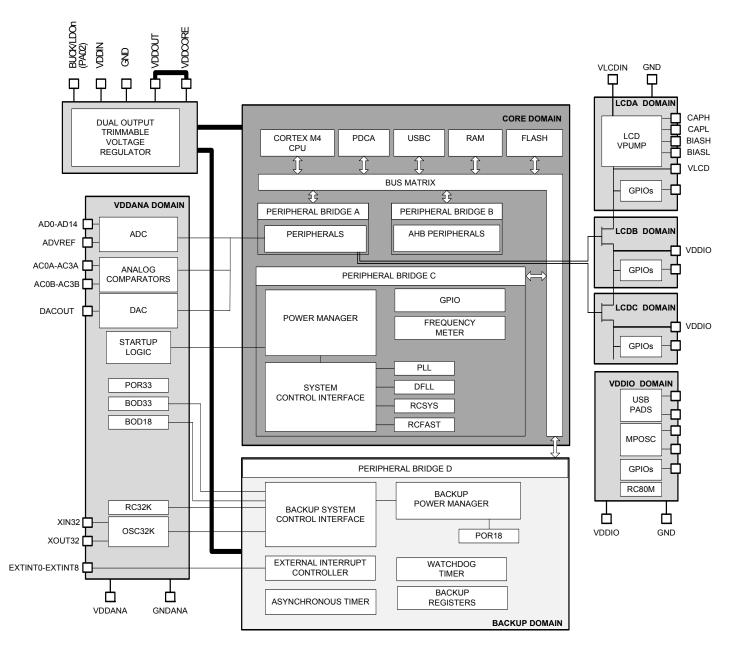

## 2. Overview

## 2.1 Block Diagram

## 2.2 Configuration Summary

Table 2-1.Sub Series Summary

| Feature     | ATSAM4LC      | ATSAM4LS    |

|-------------|---------------|-------------|

| SEGMENT LCD | Yes           | No          |

| AESA        | Yes           | No          |

| USB         | Device + Host | Device Only |

Table 2-2.Configuration Summary

| Feature                 | ATSAM4LxxC/         | ATSAM4LxxB          | ATSAM4LxxA                   |

|-------------------------|---------------------|---------------------|------------------------------|

| Number of Pins          | 100                 | 64                  | 48                           |

| Max Frequency           |                     | 48MHz               |                              |

| Flash                   |                     | 256/128KB           |                              |

| SRAM                    |                     | 32KB                |                              |

| SEGMENT LCD             | 4x40 <sup>(1)</sup> | 4x23 <sup>(1)</sup> | 4x13 <sup>(1)</sup>          |

| GPIO                    | 75 <sup>(1)</sup>   | 43 <sup>(1)</sup>   | 27 <sup>(1)</sup>            |

| High-drive pins         | 6                   | 3                   | 1                            |

| External Interrupts     |                     | 8 + 1 NMI           |                              |

| TWI                     | 2 Masters + 2 M     | Aasters/Slaves      | 1 Master + 1<br>Master/Slave |

| USART                   | 4                   |                     | 3                            |

| PICOUART                |                     | 1                   |                              |

| Peripheral DMA Channels |                     | 16                  |                              |

| AESA                    |                     | 1                   |                              |

| Peripheral Event System |                     | 1                   |                              |

| SPI                     |                     | 1                   |                              |

| Asynchronous Timers     |                     | 1                   |                              |

| Timer/Counter Channels  | 6                   |                     | 3                            |

| Parallel Capture Inputs |                     | 8                   |                              |

| Frequency Meter         |                     | 1                   |                              |

| Watchdog Timer          |                     | 1                   |                              |

| Power Manager           |                     | 1                   |                              |

| Glue Logic LUT          | 2                   |                     | 1                            |

| Feature             | ATSAM4LxxC/    | ATSAM4LxxB             | ATSAM4LxxA    |

|---------------------|----------------|------------------------|---------------|

|                     | Digital Freque | ncy Locked Loop 20-1   | 150MHz (DFLL) |

|                     | Phase L        | ocked Loop 48-240      | IHz (PLL)     |

|                     | Crystal        | Oscillator 0.6-30 MHz  | z (OSC0)      |

| Oscillators         | Crysta         | al Oscillator 32kHz (O | SC32K)        |

| Oscillators         | RC             | Oscillator 80MHz (RC   | C80M)         |

|                     | RC Os          | cillator 4,8,12MHz (R  | CFAST)        |

|                     | RC             | Oscillator 115kHz (RC  | CSYS)         |

|                     | RC             | Oscillator 32 kHz (RC  | 32K)          |

| ADC                 | 15-channel     | 7-channel              | 3-channel     |

| DAC                 |                | 1-channel              |               |

| Analog Comparators  | 4              | 2                      | 1             |

| CATB Sensors        | 32             | 32                     | 26            |

| USB                 |                | 1                      |               |

| Audio Bitstream DAC |                | 1                      |               |

| IIS Controller      |                | 1                      |               |

| Packages            | TQFP/VFBGA     | TQFP/QFN               | TQFP/QFN      |

#### Table 2-2. Configuration Summary

Notes: 1. For ATSAM4LS sub serie, no LCD SEGMENT pins are available and 5 additionnal GPIO pins are available.

- Atmel

## 3. Package and Pinout

### 3.1 Package

The device pins are multiplexed with peripheral functions as described in Section 3.2 "Peripheral Multiplexing on I/O lines" on page 16.

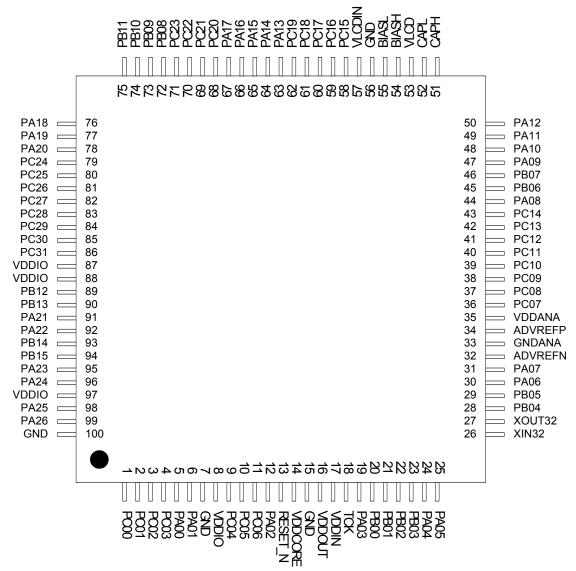

#### 3.1.1 ATSAM4LCx Pinout

Atmel

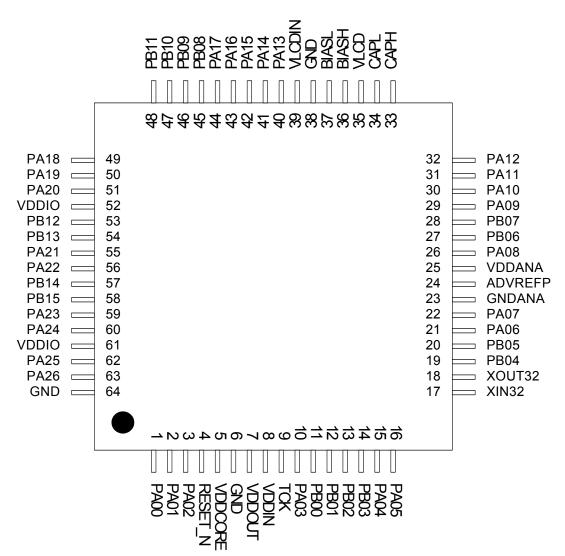

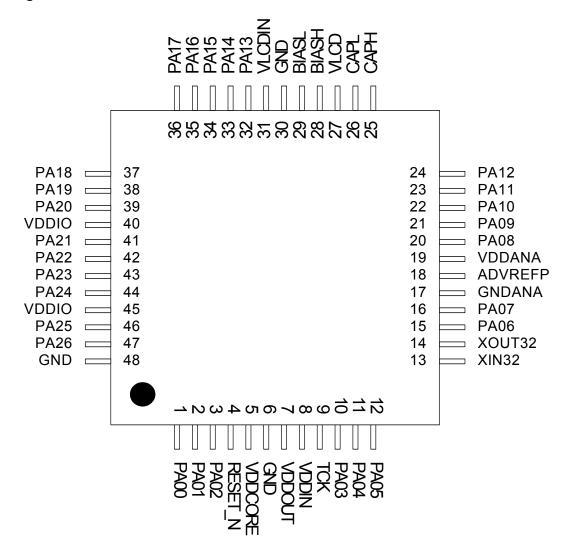

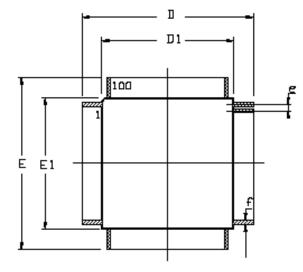

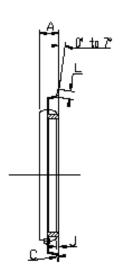

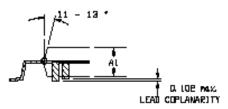

#### Figure 3-1. ATSAM4LC TQFP100 Pinout

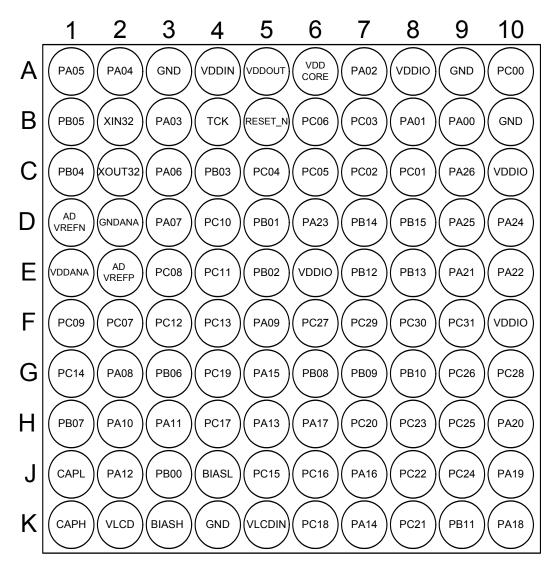

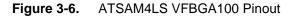

#### Figure 3-2. ATSAM4LC VFBGA100 Pinout

Atmel

Atmel

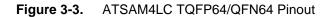

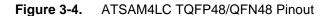

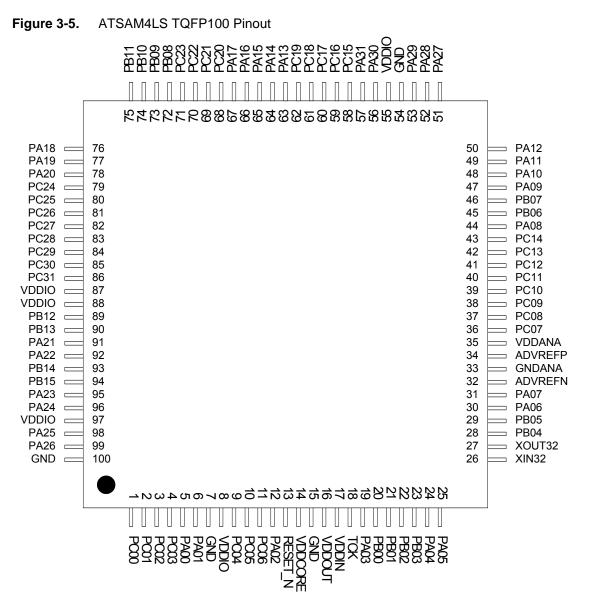

#### 3.1.2 ATSAM4LSx Pinout

Atmel

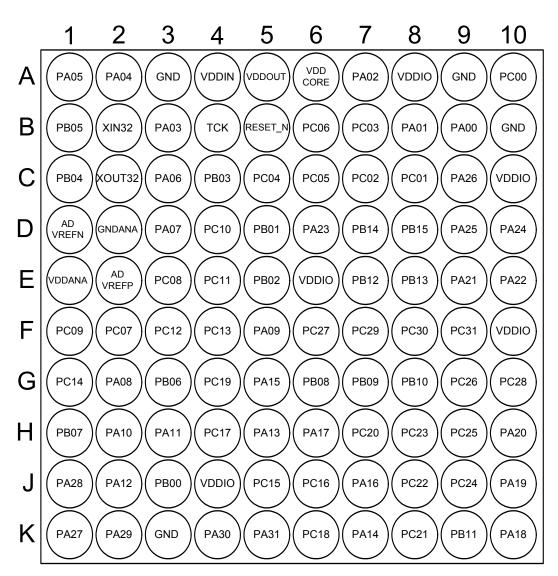

Figure 3-7. ATSAM4LS TQFP64/QFN64 Pinout

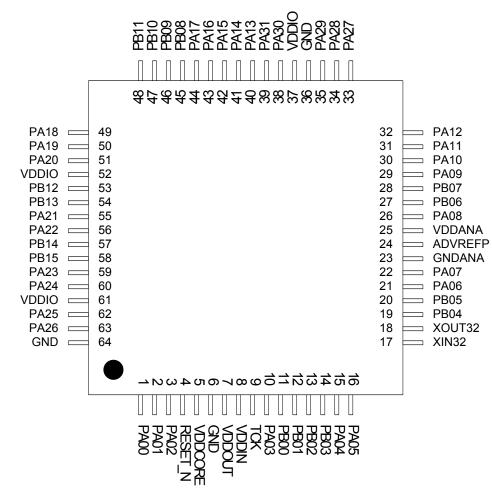

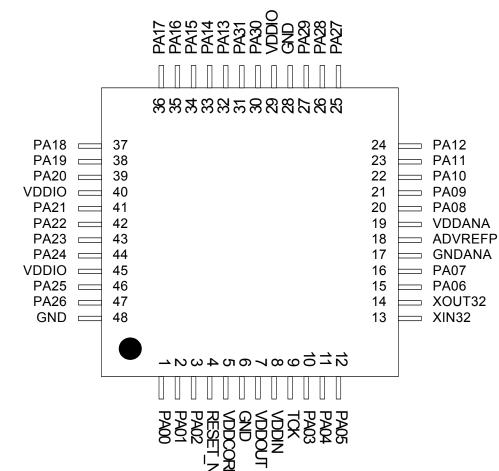

Figure 3-8. ATSAM4LS TQFP48/QFN48 Pinout

See Section 3.3 "Signals Description" on page 25 for a description of the various peripheral signals.

Refer to "Electrical Characteristics" on page 92 for a description of the electrical properties of the pin types used.

## 3.2 Peripheral Multiplexing on I/O lines

#### 3.2.1 Multiplexed Signals

Each GPIO line can be assigned to one of the peripheral functions. The following tables (Section 3-1 "100-pin GPIO Controller Function Multiplexing" on page 16 to Section 3-3 "48-pin GPIO Controller Function Multiplexing" on page 22) describes the peripheral signals multiplexed to the GPIO lines.

Peripheral functions that are not relevant in some parts of the family are grey-shaded.

For description of differents Supply voltage source, refer to the Section 6. "Power and Startup Considerations" on page 39.

Table 3-1.

100-pin GPIO Controller Function Multiplexing (Sheet 1 of 4)

| Table | •        |     |          | 0 0011 | 101101 | i anotion | manapion      | ng (oneer     |                  |                 |                   |                |                 |

|-------|----------|-----|----------|--------|--------|-----------|---------------|---------------|------------------|-----------------|-------------------|----------------|-----------------|

|       | ATSAM4LC |     | ATSAM4LS | Pin    | GPIO   | Supply    |               |               | G                | PIO Function    | ns                |                |                 |

| QFN   | VFBGA    | QFN | VFBGA    |        |        |           | Α             | В             | С                | D               | E                 | F              | G               |

| 5     | B9       | 5   | B9       | PA00   | 0      | VDDIO     |               |               |                  |                 |                   |                |                 |

| 6     | B8       | 6   | B8       | PA01   | 1      | VDDIO     |               |               |                  |                 |                   |                |                 |

| 12    | A7       | 12  | A7       | PA02   | 2      | VDDIN     | SCIF<br>GCLK0 | SPI<br>NPCS0  |                  |                 |                   |                | CATB<br>DIS     |

| 19    | B3       | 19  | B3       | PA03   | 3      | VDDIN     |               | SPI<br>MISO   |                  |                 |                   |                |                 |

| 24    | A2       | 24  | A2       | PA04   | 4      | VDDANA    | ADCIFE<br>AD0 | USART0<br>CLK | EIC<br>EXTINT2   | GLOC<br>IN1     |                   |                | CATB<br>SENSE0  |

| 25    | A1       | 25  | A1       | PA05   | 5      | VDDANA    | ADCIFE<br>AD1 | USART0<br>RXD | EIC<br>EXTINT3   | GLOC<br>IN2     | ADCIFE<br>TRIGGER |                | CATB<br>SENSE1  |

| 30    | C3       | 30  | СЗ       | PA06   | 6      | VDDANA    | DACC<br>VOUT  | USART0<br>RTS | EIC<br>EXTINT1   | GLOC<br>IN0     | ACIFC<br>ACAN0    |                | CATB<br>SENSE2  |

| 31    | D3       | 31  | D3       | PA07   | 7      | VDDANA    | ADCIFE<br>AD2 | USART0<br>TXD | EIC<br>EXTINT4   | GLOC<br>IN3     | ACIFC<br>ACAP0    |                | CATB<br>SENSE3  |

| 44    | G2       | 44  | G2       | PA08   | 8      | LCDA      | USART0<br>RTS | TC0<br>A0     | PEVC<br>PAD EVT0 | GLOC<br>OUT0    |                   | LCDCA<br>SEG23 | CATB<br>SENSE4  |

| 47    | F5       | 47  | F5       | PA09   | 9      | LCDA      | USART0<br>CTS | TC0<br>B0     | PEVC<br>PAD EVT1 | PARC<br>PCDATA0 |                   | LCDCA<br>COM3  | CATB<br>SENSE5  |

| 48    | H2       | 48  | H2       | PA10   | 10     | LCDA      | USART0<br>CLK | TC0<br>A1     | PEVC<br>PAD EVT2 | PARC<br>PCDATA1 |                   | LCDCA<br>COM2  | CATB<br>SENSE6  |

| 49    | H3       | 49  | H3       | PA11   | 11     | LCDA      | USART0<br>RXD | TC0<br>B1     | PEVC<br>PAD EVT3 | PARC<br>PCDATA2 |                   | LCDCA<br>COM1  | CATB<br>SENSE7  |

| 50    | J2       | 50  | J2       | PA12   | 12     | LCDA      | USART0<br>TXD | TC0<br>A2     |                  | PARC<br>PCDATA3 |                   | LCDCA<br>COM0  | CATB<br>DIS     |

| 63    | Н5       | 63  | H5       | PA13   | 13     | LCDA      | USART1<br>RTS | TC0<br>B2     | SPI<br>NPCS1     | PARC<br>PCDATA4 |                   | LCDCA<br>SEG5  | CATB<br>SENSE8  |

| 64    | К7       | 64  | K7       | PA14   | 14     | LCDA      | USART1<br>CLK | TC0<br>CLK0   | SPI<br>NPCS2     | PARC<br>PCDATA5 |                   | LCDCA<br>SEG6  | CATB<br>SENSE9  |

| 65    | G5       | 65  | G5       | PA15   | 15     | LCDA      | USART1<br>RXD | TC0<br>CLK1   | SPI<br>NPCS3     | PARC<br>PCDATA6 |                   | LCDCA<br>SEG7  | CATB<br>SENSE10 |

Table 3-1.

100-pin GPIO Controller Function Multiplexing (Sheet 2 of 4)

|     | ATSAM4LC |     | ATSAM4LS | Pin  | GPIO | Supply |                |                 | G               | PIO Functio     | ns                |                |                 |

|-----|----------|-----|----------|------|------|--------|----------------|-----------------|-----------------|-----------------|-------------------|----------------|-----------------|

| QFN | VFBGA    | QFN | VFBGA    |      |      |        | Α              | В               | С               | D               | E                 | F              | G               |

| 66  | J7       | 66  | J7       | PA16 | 16   | LCDA   | USART1<br>TXD  | TC0<br>CLK2     | EIC<br>EXTINT1  | PARC<br>PCDATA7 |                   | LCDCA<br>SEG8  | CATB<br>SENSE11 |

| 67  | H6       | 67  | H6       | PA17 | 17   | LCDA   | USART2<br>RTS  | ABDACB<br>DAC0  | EIC<br>EXTINT2  | PARC<br>PCCK    |                   | LCDCA<br>SEG9  | CATB<br>SENSE12 |

| 76  | K10      | 76  | K10      | PA18 | 18   | LCDA   | USART2<br>CLK  | ABDACB<br>DACN0 | EIC<br>EXTINT3  | PARC<br>PCEN1   |                   | LCDCA<br>SEG18 | CATB<br>SENSE13 |

| 77  | J10      | 77  | J10      | PA19 | 19   | LCDA   | USART2<br>RXD  | ABDACB<br>DAC1  | EIC<br>EXTINT4  | PARC<br>PCEN2   | SCIF<br>GCLK0     | LCDCA<br>SEG19 | CATB<br>SENSE14 |

| 78  | H10      | 78  | H10      | PA20 | 20   | LCDA   | USART2<br>TXD  | ABDACB<br>DACN1 | EIC<br>EXTINT5  | GLOC<br>IN0     | SCIF<br>GCLK1     | LCDCA<br>SEG20 | CATB<br>SENSE15 |

| 91  | E9       | 91  | E9       | PA21 | 21   | LCDC   | SPI<br>MISO    | USART1<br>CTS   | EIC<br>EXTINT6  | GLOC<br>IN1     | TWIM2<br>TWD      | LCDCA<br>SEG34 | CATB<br>SENSE16 |

| 92  | E10      | 92  | E10      | PA22 | 22   | LCDC   | SPI<br>MOSI    | USART2<br>CTS   | EIC<br>EXTINT7  | GLOC<br>IN2     | TWIM2<br>TWCK     | LCDCA<br>SEG35 | CATB<br>SENSE17 |

| 95  | D6       | 95  | D6       | PA23 | 23   | LCDC   | SPI<br>SCK     | TWIMS0<br>TWD   | EIC<br>EXTINT8  | GLOC<br>IN3     | SCIF<br>GCLK IN0  | LCDCA<br>SEG38 | CATB<br>DIS     |

| 96  | D10      | 96  | D10      | PA24 | 24   | LCDC   | SPI<br>NPCS0   | TWIMS0<br>TWCK  |                 | GLOC<br>OUT0    | SCIF<br>GCLK IN1  | LCDCA<br>SEG39 | CATB<br>SENSE18 |

| 98  | D9       | 98  | D9       | PA25 | 25   | VDDIO  | USBC<br>DM     | USART2<br>RXD   |                 |                 |                   |                | CATB<br>SENSE19 |

| 99  | C9       | 99  | C9       | PA26 | 26   | VDDIO  | USBC<br>DP     | USART2<br>TXD   |                 |                 |                   |                | CATB<br>SENSE20 |

|     |          | 51  | K1       | PA27 | 27   | LCDA   | SPI<br>MISO    | IISC<br>ISCK    | ABDACB<br>DAC0  | GLOC<br>IN4     | USART3<br>RTS     |                | CATB<br>SENSE0  |

|     |          | 52  | J1       | PA28 | 28   | LCDA   | SPI<br>MOSI    | IISC<br>ISDI    | ABDACB<br>DACN0 | GLOC<br>IN5     | USART3<br>CTS     |                | CATB<br>SENSE1  |

|     |          | 53  | K2       | PA29 | 29   | LCDA   | SPI<br>SCK     | IISC<br>IWS     | ABDACB<br>DAC1  | GLOC<br>IN6     | USART3<br>CLK     |                | CATB<br>SENSE2  |

|     |          | 56  | K4       | PA30 | 30   | LCDA   | SPI<br>NPCS0   | IISC<br>ISDO    | ABDACB<br>DACN1 | GLOC<br>IN7     | USART3<br>RXD     |                | CATB<br>SENSE3  |

|     |          | 57  | K5       | PA31 | 31   | LCDA   | SPI<br>NPCS1   | IISC<br>IMCK    | ABDACB<br>CLK   | GLOC<br>OUT1    | USART3<br>TXD     |                | CATB<br>DIS     |

| 20  | J3       | 20  | J3       | PB00 | 32   | VDDIN  | TWIMS1<br>TWD  | USART0<br>RXD   |                 |                 |                   |                | CATB<br>SENSE21 |

| 21  | D5       | 21  | D5       | PB01 | 33   | VDDIN  | TWIMS1<br>TWCK | USART0<br>TXD   | EIC<br>EXTINT0  |                 |                   |                | CATB<br>SENSE22 |

| 22  | E5       | 22  | E5       | PB02 | 34   | VDDANA | ADCIFE<br>AD3  | USART1<br>RTS   | ABDACB<br>DAC0  | IISC<br>ISCK    | ACIFC<br>ACBN0    |                | CATB<br>SENSE23 |

| 23  | C4       | 23  | C4       | PB03 | 35   | VDDANA | ADCIFE<br>AD4  | USART1<br>CLK   | ABDACB<br>DACN0 | IISC<br>ISDI    | ACIFC<br>ACBP0    |                | CATB<br>DIS     |

| 28  | C1       | 28  | C1       | PB04 | 36   | VDDANA | ADCIFE<br>AD5  | USART1<br>RXD   | ABDACB<br>DAC1  | IISC<br>ISDO    | DACC<br>EXT TRIG0 |                | CATB<br>SENSE24 |

| 29  | B1       | 29  | B1       | PB05 | 37   | VDDANA | ADCIFE<br>AD6  | USART1<br>TXD   | ABDACB<br>DACN1 | IISC<br>IMCK    |                   |                | CATB<br>SENSE25 |

| 45  | G3       | 45  | G3       | PB06 | 38   | LCDA   | USART3<br>RTS  |                 | GLOC<br>IN4     | IISC<br>IWS     |                   | LCDCA<br>SEG22 | CATB<br>SENSE26 |

| 46  | H1       | 46  | H1       | PB07 | 39   | LCDA   | USART3<br>CTS  |                 | GLOC<br>IN5     | TC0<br>A0       |                   | LCDCA<br>SEG21 | CATB<br>SENSE27 |

Table 3-1.

100-pin GPIO Controller Function Multiplexing (Sheet 3 of 4)

|     | ATSAM4LC |     | ATSAM4LS | Pin  | GPIO | Supply |                | 3 (              | GI               | PIO Functio  | ns               |                |                 |

|-----|----------|-----|----------|------|------|--------|----------------|------------------|------------------|--------------|------------------|----------------|-----------------|

| QFN | VFBGA    | QFN | VFBGA    |      |      |        | Α              | В                | С                | D            | E                | F              | G               |

| 72  | G6       | 72  | G6       | PB08 | 40   | LCDA   | USART3<br>CLK  |                  | GLOC<br>IN6      | ТС0<br>В0    |                  | LCDCA<br>SEG14 | CATB<br>SENSE28 |

| 73  | G7       | 73  | G7       | PB09 | 41   | LCDA   | USART3<br>RXD  | PEVC<br>PAD EVT2 | GLOC<br>IN7      | TC0<br>A1    |                  | LCDCA<br>SEG15 | CATB<br>SENSE29 |

| 74  | G8       | 74  | G8       | PB10 | 42   | LCDA   | USART3<br>TXD  | PEVC<br>PAD EVT3 | GLOC<br>OUT1     | TC0<br>B1    | SCIF<br>GCLK0    | LCDCA<br>SEG16 | CATB<br>SENSE30 |

| 75  | К9       | 75  | К9       | PB11 | 43   | LCDA   | USART0<br>CTS  | SPI<br>NPCS2     |                  | TC0<br>A2    | SCIF<br>GCLK1    | LCDCA<br>SEG17 | CATB<br>SENSE31 |

| 89  | E7       | 89  | E7       | PB12 | 44   | LCDC   | USART0<br>RTS  | SPI<br>NPCS3     | PEVC<br>PAD EVT0 | TC0<br>B2    | SCIF<br>GCLK2    | LCDCA<br>SEG32 | CATB<br>DIS     |

| 90  | E8       | 90  | E8       | PB13 | 45   | LCDC   | USART0<br>CLK  | SPI<br>NPCS1     | PEVC<br>PAD EVT1 | TC0<br>CLK0  | SCIF<br>GCLK3    | LCDCA<br>SEG33 | CATB<br>SENSE0  |

| 93  | D7       | 93  | D7       | PB14 | 46   | LCDC   | USART0<br>RXD  | SPI<br>MISO      | TWIM3<br>TWD     | TC0<br>CLK1  | SCIF<br>GCLK IN0 | LCDCA<br>SEG36 | CATB<br>SENSE1  |

| 94  | D8       | 94  | D8       | PB15 | 47   | LCDC   | USART0<br>TXD  | SPI<br>MOSI      | TWIM3<br>TWCK    | TC0<br>CLK2  | SCIF<br>GCLK IN1 | LCDCA<br>SEG37 | CATB<br>SENSE2  |

| 1   | A10      | 1   | A10      | PC00 | 64   | VDDIO  | SPI<br>NPCS2   | USART0<br>CLK    |                  | TC1<br>A0    |                  |                | CATB<br>SENSE3  |

| 2   | C8       | 2   | C8       | PC01 | 65   | VDDIO  | SPI<br>NPCS3   | USART0<br>RTS    |                  | TC1<br>B0    |                  |                | CATB<br>SENSE4  |

| 3   | C7       | 3   | C7       | PC02 | 66   | VDDIO  | SPI<br>NPCS1   | USART0<br>CTS    | USART0<br>RXD    | TC1<br>A1    |                  |                | CATB<br>SENSE5  |

| 4   | B7       | 4   | B7       | PC03 | 67   | VDDIO  | SPI<br>NPCS0   | EIC<br>EXTINT5   | USART0<br>TXD    | TC1<br>B1    |                  |                | CATB<br>SENSE6  |

| 9   | C5       | 9   | C5       | PC04 | 68   | VDDIO  | SPI<br>MISO    | EIC<br>EXTINT6   |                  | TC1<br>A2    |                  |                | CATB<br>SENSE7  |

| 10  | C6       | 10  | C6       | PC05 | 69   | VDDIO  | SPI<br>MOSI    | EIC<br>EXTINT7   |                  | TC1<br>B2    |                  |                | CATB<br>DIS     |

| 11  | B6       | 11  | B6       | PC06 | 70   | VDDIO  | SPI<br>SCK     | EIC<br>EXTINT8   |                  | TC1<br>CLK0  |                  |                | CATB<br>SENSE8  |

| 36  | F2       | 36  | F2       | PC07 | 71   | VDDANA | ADCIFE<br>AD7  | USART2<br>RTS    | PEVC<br>PAD EVT0 | TC1<br>CLK1  |                  |                | CATB<br>SENSE9  |

| 37  | E3       | 37  | E3       | PC08 | 72   | VDDANA | ADCIFE<br>AD8  | USART2<br>CLK    | PEVC<br>PAD EVT1 | TC1<br>CLK2  | USART2<br>CTS    |                | CATB<br>SENSE10 |

| 38  | F1       | 38  | F1       | PC09 | 73   | VDDANA | ADCIFE<br>AD9  | USART3<br>RXD    | ABDACB<br>DAC0   | IISC<br>ISCK | ACIFC<br>ACAN1   |                | CATB<br>SENSE11 |

| 39  | D4       | 39  | D4       | PC10 | 74   | VDDANA | ADCIFE<br>AD10 | USART3<br>TXD    | ABDACB<br>DACN0  | IISC<br>ISDI | ACIFC<br>ACAP1   |                | CATB<br>SENSE12 |

| 40  | E4       | 40  | E4       | PC11 | 75   | VDDANA | ADCIFE<br>AD11 | USART2<br>RXD    | PEVC<br>PAD EVT2 |              |                  |                | CATB<br>SENSE13 |

| 41  | F3       | 41  | F3       | PC12 | 76   | VDDANA | ADCIFE<br>AD12 | USART2<br>TXD    | ABDACB<br>CLK    | IISC<br>IWS  |                  |                | CATB<br>SENSE14 |

| 42  | F4       | 42  | F4       | PC13 | 77   | VDDANA | ADCIFE<br>AD13 | USART3<br>RTS    | ABDACB<br>DAC1   | IISC<br>ISDO | ACIFC<br>ACBN1   |                | CATB<br>SENSE15 |

| 43  | G1       | 43  | G1       | PC14 | 78   | VDDANA | ADCIFE<br>AD14 | USART3<br>CLK    | ABDACB<br>DACN1  | IISC<br>IMCK | ACIFC<br>ACBP1   |                | CATB<br>DIS     |

| 58  | J5       | 58  | J5       | PC15 | 79   | LCDA   | TC1<br>A0      |                  |                  | GLOC<br>IN4  |                  | LCDCA<br>SEG0  | CATB<br>SENSE16 |

Table 3-1.

100-pin GPIO Controller Function Multiplexing (Sheet 4 of 4)

|     | ATSAM4LC |     | ATSAM4LS | Pin  | GPIO | Supply | Aiddine       |                | G                | GPIO Functions  |                  |                |                 |

|-----|----------|-----|----------|------|------|--------|---------------|----------------|------------------|-----------------|------------------|----------------|-----------------|

| QFN | VFBGA    | QFN | VFBGA    |      |      |        | Α             | В              | С                | D               | E                | F              | G               |

| 59  | J6       | 59  | J6       | PC16 | 80   | LCDA   | TC1<br>B0     |                |                  | GLOC<br>IN5     |                  | LCDCA<br>SEG1  | CATB<br>SENSE17 |

| 60  | H4       | 60  | H4       | PC17 | 81   | LCDA   | TC1<br>A1     |                |                  | GLOC<br>IN6     |                  | LCDCA<br>SEG2  | CATB<br>SENSE18 |

| 61  | K6       | 61  | K6       | PC18 | 82   | LCDA   | TC1<br>B1     |                |                  | GLOC<br>IN7     |                  | LCDCA<br>SEG3  | CATB<br>SENSE19 |

| 62  | G4       | 62  | G4       | PC19 | 83   | LCDA   | TC1<br>A2     |                |                  | GLOC<br>OUT1    |                  | LCDCA<br>SEG4  | CATB<br>SENSE20 |

| 68  | H7       | 68  | H7       | PC20 | 84   | LCDA   | TC1<br>B2     |                |                  |                 |                  | LCDCA<br>SEG10 | CATB<br>SENSE21 |

| 69  | К8       | 69  | K8       | PC21 | 85   | LCDA   | TC1<br>CLK0   |                |                  | PARC<br>PCCK    |                  | LCDCA<br>SEG11 | CATB<br>SENSE22 |

| 70  | J8       | 70  | J8       | PC22 | 86   | LCDA   | TC1<br>CLK1   |                |                  | PARC<br>PCEN1   |                  | LCDCA<br>SEG12 | CATB<br>SENSE23 |

| 71  | H8       | 71  | H8       | PC23 | 87   | LCDA   | TC1<br>CLK2   |                |                  | PARC<br>PCEN2   |                  | LCDCA<br>SEG13 | CATB<br>DIS     |

| 79  | J9       | 79  | J9       | PC24 | 88   | LCDB   | USART1<br>RTS | EIC<br>EXTINT1 | PEVC<br>PAD EVT0 | PARC<br>PCDATA0 |                  | LCDCA<br>SEG24 | CATB<br>SENSE24 |

| 80  | H9       | 80  | H9       | PC25 | 89   | LCDB   | USART1<br>CLK | EIC<br>EXTINT2 | PEVC<br>PAD EVT1 | PARC<br>PCDATA1 |                  | LCDCA<br>SEG25 | CATB<br>SENSE25 |

| 81  | G9       | 81  | G9       | PC26 | 90   | LCDB   | USART1<br>RXD | EIC<br>EXTINT3 | PEVC<br>PAD EVT2 | PARC<br>PCDATA2 | SCIF<br>GCLK0    | LCDCA<br>SEG26 | CATB<br>SENSE26 |

| 82  | F6       | 82  | F6       | PC27 | 91   | LCDB   | USART1<br>TXD | EIC<br>EXTINT4 | PEVC<br>PAD EVT3 | PARC<br>PCDATA3 | SCIF<br>GCLK1    | LCDCA<br>SEG27 | CATB<br>SENSE27 |

| 83  | G10      | 83  | G10      | PC28 | 92   | LCDB   | USART3<br>RXD | SPI<br>MISO    | GLOC<br>IN4      | PARC<br>PCDATA4 | SCIF<br>GCLK2    | LCDCA<br>SEG28 | CATB<br>SENSE28 |

| 84  | F7       | 84  | F7       | PC29 | 93   | LCDB   | USART3<br>TXD | SPI<br>MOSI    | GLOC<br>IN5      | PARC<br>PCDATA5 | SCIF<br>GCLK3    | LCDCA<br>SEG29 | CATB<br>SENSE29 |

| 85  | F8       | 85  | F8       | PC30 | 94   | LCDB   | USART3<br>RTS | SPI<br>SCK     | GLOC<br>IN6      | PARC<br>PCDATA6 | SCIF<br>GCLK IN0 | LCDCA<br>SEG30 | CATB<br>SENSE30 |

| 86  | F9       | 86  | F9       | PC31 | 95   | LCDB   | USART3<br>CLK | SPI<br>NPCS0   | GLOC<br>OUT1     | PARC<br>PCDATA7 | SCIF<br>GCLK IN1 | LCDCA<br>SEG31 | CATB<br>SENSE31 |

Table 3-2.

64-pin GPIO Controller Function Multiplexing (Sheet 1 of 3)

| ATSAM4LC | ATSAM4LS | Pin  | GPIO | Supply |               |              | G | PIO Functio | ns |   |             |

|----------|----------|------|------|--------|---------------|--------------|---|-------------|----|---|-------------|

| QFP      | QFP      |      | -    | S      |               |              |   |             |    |   |             |

| QFN      | QFN      |      |      |        | Α             | В            | С | D           | E  | F | G           |

| 1        | 1        | PA00 | 0    | VDDIO  |               |              |   |             |    |   |             |

| 2        | 2        | PA01 | 1    | VDDIO  |               |              |   |             |    |   |             |

| 3        | 3        | PA02 | 2    | VDDIN  | SCIF<br>GCLK0 | SPI<br>NPCS0 |   |             |    |   | CATB<br>DIS |

| 10       | 10       | PA03 | 3    | VDDIN  |               | SPI<br>MISO  |   |             |    |   |             |

Table 3-2.

64-pin GPIO Controller Function Multiplexing (Sheet 2 of 3)

| ATSAM4LC | ATSAM4LS | Pin  | GPIO | Supply |               |                 | G                | PIO Function    | ns                |                |                 |

|----------|----------|------|------|--------|---------------|-----------------|------------------|-----------------|-------------------|----------------|-----------------|

| QFP      | QFP      |      | 0    | Ñ      | _             | _               | _                | _               |                   | _              | _               |

| QFN      | QFN      |      |      |        | A             | В               | С                | D               | E                 | F              | G               |

| 15       | 15       | PA04 | 4    | VDDANA | ADCIFE<br>AD0 | USART0<br>CLK   | EIC<br>EXTINT2   | GLOC<br>IN1     |                   |                | CATB<br>SENSE0  |

| 16       | 16       | PA05 | 5    | VDDANA | ADCIFE<br>AD1 | USART0<br>RXD   | EIC<br>EXTINT3   | GLOC<br>IN2     | ADCIFE<br>TRIGGER |                | CATB<br>SENSE1  |

| 21       | 21       | PA06 | 6    | VDDANA | DACC<br>VOUT  | USART0<br>RTS   | EIC<br>EXTINT1   | GLOC<br>IN0     | ACIFC<br>ACAN0    |                | CATB<br>SENSE2  |

| 22       | 22       | PA07 | 7    | VDDANA | ADCIFE<br>AD2 | USART0<br>TXD   | EIC<br>EXTINT4   | GLOC<br>IN3     | ACIFC<br>ACAP0    |                | CATB<br>SENSE3  |

| 26       | 26       | PA08 | 8    | LCDA   | USART0<br>RTS | TC0<br>A0       | PEVC<br>PAD EVT0 | GLOC<br>OUT0    |                   | LCDCA<br>SEG23 | CATB<br>SENSE4  |

| 29       | 29       | PA09 | 9    | LCDA   | USART0<br>CTS | ТС0<br>В0       | PEVC<br>PAD EVT1 | PARC<br>PCDATA0 |                   | LCDCA<br>COM3  | CATB<br>SENSE5  |

| 30       | 30       | PA10 | 10   | LCDA   | USART0<br>CLK | TC0<br>A1       | PEVC<br>PAD EVT2 | PARC<br>PCDATA1 |                   | LCDCA<br>COM2  | CATB<br>SENSE6  |

| 31       | 31       | PA11 | 11   | LCDA   | USART0<br>RXD | TC0<br>B1       | PEVC<br>PAD EVT3 | PARC<br>PCDATA2 |                   | LCDCA<br>COM1  | CATB<br>SENSE7  |

| 32       | 32       | PA12 | 12   | LCDA   | USART0<br>TXD | TC0<br>A2       |                  | PARC<br>PCDATA3 |                   | LCDCA<br>COM0  | CATB<br>DIS     |

| 40       | 40       | PA13 | 13   | LCDA   | USART1<br>RTS | TC0<br>B2       | SPI<br>NPCS1     | PARC<br>PCDATA4 |                   | LCDCA<br>SEG5  | CATB<br>SENSE8  |

| 41       | 41       | PA14 | 14   | LCDA   | USART1<br>CLK | TC0<br>CLK0     | SPI<br>NPCS2     | PARC<br>PCDATA5 |                   | LCDCA<br>SEG6  | CATB<br>SENSE9  |

| 42       | 42       | PA15 | 15   | LCDA   | USART1<br>RXD | TC0<br>CLK1     | SPI<br>NPCS3     | PARC<br>PCDATA6 |                   | LCDCA<br>SEG7  | CATB<br>SENSE10 |

| 43       | 43       | PA16 | 16   | LCDA   | USART1<br>TXD | TC0<br>CLK2     | EIC<br>EXTINT1   | PARC<br>PCDATA7 |                   | LCDCA<br>SEG8  | CATB<br>SENSE11 |

| 44       | 44       | PA17 | 17   | LCDA   | USART2<br>RTS | ABDACB<br>DAC0  | EIC<br>EXTINT2   | PARC<br>PCCK    |                   | LCDCA<br>SEG9  | CATB<br>SENSE12 |

| 49       | 49       | PA18 | 18   | LCDA   | USART2<br>CLK | ABDACB<br>DACN0 | EIC<br>EXTINT3   | PARC<br>PCEN1   |                   | LCDCA<br>SEG18 | CATB<br>SENSE13 |

| 50       | 50       | PA19 | 19   | LCDA   | USART2<br>RXD | ABDACB<br>DAC1  | EIC<br>EXTINT4   | PARC<br>PCEN2   | SCIF<br>GCLK0     | LCDCA<br>SEG19 | CATB<br>SENSE14 |

| 51       | 51       | PA20 | 20   | LCDA   | USART2<br>TXD | ABDACB<br>DACN1 | EIC<br>EXTINT5   | GLOC<br>IN0     | SCIF<br>GCLK1     | LCDCA<br>SEG20 | CATB<br>SENSE15 |

| 55       | 55       | PA21 | 21   | LCDC   | SPI<br>MISO   | USART1<br>CTS   | EIC<br>EXTINT6   | GLOC<br>IN1     | TWIM2<br>TWD      | LCDCA<br>SEG34 | CATB<br>SENSE16 |

| 56       | 56       | PA22 | 22   | LCDC   | SPI<br>MOSI   | USART2<br>CTS   | EIC<br>EXTINT7   | GLOC<br>IN2     | TWIM2<br>TWCK     | LCDCA<br>SEG35 | CATB<br>SENSE17 |

| 59       | 59       | PA23 | 23   | LCDC   | SPI<br>SCK    | TWIMS0<br>TWD   | EIC<br>EXTINT8   | GLOC<br>IN3     | SCIF<br>GCLK IN0  | LCDCA<br>SEG38 | CATB<br>DIS     |

| 60       | 60       | PA24 | 24   | LCDC   | SPI<br>NPCS0  | TWIMS0<br>TWCK  |                  | GLOC<br>OUT0    | SCIF<br>GCLK IN1  | LCDCA<br>SEG39 | CATB<br>SENSE18 |

| 62       | 62       | PA25 | 25   | VDDIO  | USBC<br>DM    | USART2<br>RXD   |                  |                 |                   |                | CATB<br>SENSE19 |

| 63       | 63       | PA26 | 26   | VDDIO  | USBC<br>DP    | USART2<br>TXD   |                  |                 |                   |                | CATB<br>SENSE20 |

Table 3-2.

64-pin GPIO Controller Function Multiplexing (Sheet 3 of 3)

| ATSAM4LC   | ATSAM4LS   | Pin  | GPIO | Supply |                |                  | GI               | PIO Functio  | ns                |                |                 |

|------------|------------|------|------|--------|----------------|------------------|------------------|--------------|-------------------|----------------|-----------------|

| QFP<br>QFN | QFP<br>QFN |      |      | 0      | А              | в                | с                | D            | Е                 | F              | G               |

|            | 33         | PA27 | 27   | LCDA   | SPI<br>MISO    | IISC<br>ISCK     | ABDACB<br>DAC0   | GLOC<br>IN4  | USART3<br>RTS     |                | CATB<br>SENSE0  |

|            | 34         | PA28 | 28   | LCDA   | SPI<br>MOSI    | IISC<br>ISDI     | ABDACB<br>DACN0  | GLOC<br>IN5  | USART3<br>CTS     |                | CATB<br>SENSE1  |

|            | 35         | PA29 | 29   | LCDA   | SPI<br>SCK     | IISC<br>IWS      | ABDACB<br>DAC1   | GLOC<br>IN6  | USART3<br>CLK     |                | CATB<br>SENSE2  |

|            | 38         | PA30 | 30   | LCDA   | SPI<br>NPCS0   | IISC<br>ISDO     | ABDACB<br>DACN1  | GLOC<br>IN7  | USART3<br>RXD     |                | CATB<br>SENSE3  |

|            | 39         | PA31 | 31   | LCDA   | SPI<br>NPCS1   | IISC<br>IMCK     | ABDACB<br>CLK    | GLOC<br>OUT1 | USART3<br>TXD     |                | CATB<br>DIS     |

| 11         | 11         | PB00 | 32   | VDDIN  | TWIMS1<br>TWD  | USART0<br>RXD    |                  |              |                   |                | CATB<br>SENSE21 |

| 12         | 12         | PB01 | 33   | VDDIN  | TWIMS1<br>TWCK | USART0<br>TXD    | EIC<br>EXTINT0   |              |                   |                | CATB<br>SENSE22 |

| 13         | 13         | PB02 | 34   | VDDANA | ADCIFE<br>AD3  | USART1<br>RTS    | ABDACB<br>DAC0   | IISC<br>ISCK | ACIFC<br>ACBN0    |                | CATB<br>SENSE23 |

| 14         | 14         | PB03 | 35   | VDDANA | ADCIFE<br>AD4  | USART1<br>CLK    | ABDACB<br>DACN0  | IISC<br>ISDI | ACIFC<br>ACBP0    |                | CATB<br>DIS     |

| 19         | 19         | PB04 | 36   | VDDANA | ADCIFE<br>AD5  | USART1<br>RXD    | ABDACB<br>DAC1   | IISC<br>ISDO | DACC<br>EXT TRIG0 |                | CATB<br>SENSE24 |

| 20         | 20         | PB05 | 37   | VDDANA | ADCIFE<br>AD6  | USART1<br>TXD    | ABDACB<br>DACN1  | IISC<br>IMCK |                   |                | CATB<br>SENSE25 |

| 27         | 27         | PB06 | 38   | LCDA   | USART3<br>RTS  |                  | GLOC<br>IN4      | IISC<br>IWS  |                   | LCDCA<br>SEG22 | CATB<br>SENSE26 |

| 28         | 28         | PB07 | 39   | LCDA   | USART3<br>CTS  |                  | GLOC<br>IN5      | TC0<br>A0    |                   | LCDCA<br>SEG21 | CATB<br>SENSE27 |

| 45         | 45         | PB08 | 40   | LCDA   | USART3<br>CLK  |                  | GLOC<br>IN6      | ТС0<br>В0    |                   | LCDCA<br>SEG14 | CATB<br>SENSE28 |

| 46         | 46         | PB09 | 41   | LCDA   | USART3<br>RXD  | PEVC<br>PAD EVT2 | GLOC<br>IN7      | TC0<br>A1    |                   | LCDCA<br>SEG15 | CATB<br>SENSE29 |

| 47         | 47         | PB10 | 42   | LCDA   | USART3<br>TXD  | PEVC<br>PAD EVT3 | GLOC<br>OUT1     | TC0<br>B1    | SCIF<br>GCLK0     | LCDCA<br>SEG16 | CATB<br>SENSE30 |

| 48         | 48         | PB11 | 43   | LCDA   | USART0<br>CTS  | SPI<br>NPCS2     |                  | TC0<br>A2    | SCIF<br>GCLK1     | LCDCA<br>SEG17 | CATB<br>SENSE31 |

| 53         | 53         | PB12 | 44   | LCDC   | USART0<br>RTS  | SPI<br>NPCS3     | PEVC<br>PAD EVT0 | TC0<br>B2    | SCIF<br>GCLK2     | LCDCA<br>SEG32 | CATB<br>DIS     |

| 54         | 54         | PB13 | 45   | LCDC   | USART0<br>CLK  | SPI<br>NPCS1     | PEVC<br>PAD EVT1 | TC0<br>CLK0  | SCIF<br>GCLK3     | LCDCA<br>SEG33 | CATB<br>SENSE0  |

| 57         | 57         | PB14 | 46   | LCDC   | USART0<br>RXD  | SPI<br>MISO      | TWIM3<br>TWD     | TC0<br>CLK1  | SCIF<br>GCLK IN0  | LCDCA<br>SEG36 | CATB<br>SENSE1  |

| 58         | 58         | PB15 | 47   | LCDC   | USART0<br>TXD  | SPI<br>MOSI      | TWIM3<br>TWCK    | TC0<br>CLK2  | SCIF<br>GCLK IN1  | LCDCA<br>SEG37 | CATB<br>SENSE2  |

|          | ະ ລ-ວ.<br>ທຸ |       | P    |         |               |                 |                  |                 |                   |                |                 |

|----------|--------------|-------|------|---------|---------------|-----------------|------------------|-----------------|-------------------|----------------|-----------------|

| ATSAM4LC | ATSAM4LS     | ~     | 0    | УIС     |               |                 | GI               | PIO Functio     | ns                |                |                 |

| 3AN      | SAN          | Pin   | GPIO | Supply  |               |                 |                  |                 |                   |                |                 |

| ATS      | ATS          |       | Ŭ    | s       | Α             | В               | С                | D               | Е                 | F              | G               |

| 1        | 1            | PA00  | 0    | VDDIO   |               |                 |                  |                 |                   |                |                 |

| 2        | 2            | PA01  | 1    | VDDIO   |               |                 |                  |                 |                   |                |                 |

|          |              |       |      |         | SCIF          | SPI             |                  |                 |                   |                | CATB            |

| 3        | 3            | PA02  | 2    | VDDIN   | GCLK0         | NPCS0           |                  |                 |                   |                | DIS             |

| 10       | 10           | PA03  | 3    | VDDIN   |               | SPI<br>MISO     |                  |                 |                   |                |                 |

| 11       | 11           | PA04  | 4    | VDDANA  | ADCIFE<br>AD0 | USART0<br>CLK   | EIC<br>EXTINT2   | GLOC<br>IN1     |                   |                | CATB<br>SENSE0  |

| 12       | 12           | PA05  | 5    | VDDANA  | ADCIFE<br>AD1 | USART0<br>RXD   | EIC<br>EXTINT3   | GLOC<br>IN2     | ADCIFE<br>TRIGGER |                | CATB<br>SENSE1  |

|          | 12           | 1,400 | Ŭ    | TEEAINA | DACC          | USART0          | EIC              | GLOC            | ACIFC             |                | CATB            |

| 15       | 15           | PA06  | 6    | VDDANA  | VOUT          | RTS             | EXTINT1          | INO             | ACAN0             |                | SENSE2          |

|          |              |       |      |         | ADCIFE        | USART0          | EIC              | GLOC            | ACIFC             |                | CATB            |

| 16       | 16           | PA07  | 7    | VDDANA  | AD2           | TXD             | EXTINT4          | IN3             | ACAP0             |                | SENSE3          |

| 20       | 20           | DAGO  |      |         | USART0        | TC0             | PEVC             | GLOC            |                   | LCDCA          | CATB            |

| 20       | 20           | PA08  | 8    | LCDA    | RTS           | A0              | PAD EVTO         | OUT0            |                   | SEG23          | SENSE4          |

| 21       | 21           | PA09  | 9    | LCDA    | USART0<br>CTS | ТС0<br>В0       | PEVC<br>PAD EVT1 | PARC<br>PCDATA0 |                   | LCDCA<br>COM3  | CATB<br>SENSE5  |

|          |              |       | •    |         | USART0        | TC0             | PEVC             | PARC            |                   | LCDCA          | CATB            |

| 22       | 22           | PA10  | 10   | LCDA    | CLK           | A1              | PAD EVT2         | PCDATA1         |                   | COM2           | SENSE6          |

|          |              |       |      |         | USART0        | TC0             | PEVC             | PARC            |                   | LCDCA          | CATB            |

| 23       | 23           | PA11  | 11   | LCDA    | RXD           | B1              | PAD EVT3         | PCDATA2         |                   | COM1           | SENSE7          |

| 24       | 24           | PA12  | 12   | LCDA    | USART0<br>TXD | TC0<br>A2       |                  | PARC<br>PCDATA3 |                   | LCDCA<br>COM0  | CATB<br>DIS     |

|          |              | 1714  | .2   |         | USART1        | TC0             | SPI              | PARC            |                   | LCDCA          | CATB            |

| 32       | 32           | PA13  | 13   | LCDA    | RTS           | B2              | NPCS1            | PCDATA4         |                   | SEG5           | SENSE8          |

|          |              |       |      |         | USART1        | TC0             | SPI              | PARC            |                   | LCDCA          | CATB            |

| 33       | 33           | PA14  | 14   | LCDA    | CLK           | CLK0            | NPCS2            | PCDATA5         |                   | SEG6           | SENSE9          |

| 24       | 24           | DA45  | 15   |         | USART1        | TC0             | SPI              |                 |                   | LCDCA          |                 |

| 34       | 34           | PA15  | 15   | LCDA    | RXD           | CLK1            | NPCS3            | PCDATA6         |                   | SEG7           | SENSE10         |

| 35       | 35           | PA16  | 16   | LCDA    | USART1<br>TXD | TC0<br>CLK2     | EIC<br>EXTINT1   | PARC<br>PCDATA7 |                   | LCDCA<br>SEG8  | CATB<br>SENSE11 |

|          |              |       |      |         | USART2        | ABDACB          | EIC              | PARC            |                   | LCDCA          | CATB            |

| 36       | 36           | PA17  | 17   | LCDA    | RTS           | DAC0            | EXTINT2          | PCCK            |                   | SEG9           | SENSE12         |

| 37       | 37           | PA18  | 18   | LCDA    | USART2<br>CLK | ABDACB<br>DACN0 | EIC<br>EXTINT3   | PARC<br>PCEN1   |                   | LCDCA<br>SEG18 | CATB<br>SENSE13 |

|          |              |       |      |         | USART2        | ABDACB          | EIC              | PARC            | SCIF              | LCDCA          | CATB            |

| 38       | 38           | PA19  | 19   | LCDA    | RXD           | DAC1            | EXTINT4          | PCEN2           | GCLK0             | SEG19          | SENSE14         |

| 39       | 39           | PA20  | 20   | LCDA    | USART2<br>TXD | ABDACB<br>DACN1 | EIC<br>EXTINT5   | GLOC<br>IN0     | SCIF<br>GCLK1     | LCDCA<br>SEG20 | CATB<br>SENSE15 |

| 41       | 41           | PA21  | 21   | LCDC    | SPI<br>MISO   | USART1<br>CTS   | EIC<br>EXTINT6   | GLOC<br>IN1     | TWIM2<br>TWD      | LCDCA<br>SEG34 | CATB<br>SENSE16 |

|          |              |       |      |         | SPI           | USART2          | EIC              | GLOC            | TWIM2             | LCDCA          | САТВ            |

| 42       | 42           | PA22  | 22   | LCDC    | MOSI          | CTS             | EXTINT7          | IN2             | тюск              | SEG35          | SENSE17         |

|          | 4.5          | DAGG  |      | 1.050   | SPI           | TWIMS0          | EIC              | GLOC            | SCIF              | LCDCA          | CATB            |

| 43       | 43           | PA23  | 23   | LCDC    | SCK           | TWD             | EXTINT8          | IN3             | GCLK IN0          | SEG38          | DIS             |

**Table 3-3.**48-pin GPIO Controller Function Multiplexing (Sheet 1 of 2)

| 4LC      | 4LS      |      | PIO  | Ā              |              |                | GI              | PIO Functio  | ns               |                |                 |

|----------|----------|------|------|----------------|--------------|----------------|-----------------|--------------|------------------|----------------|-----------------|

| ATSAM4LC | ATSAM4LS | Pin  | GPIC | <b>Vidqu</b> S | A            | В              | С               | D            | E                | F              | G               |

| 44       | 44       | PA24 | 24   | LCDC           | SPI<br>NPCS0 | TWIMS0<br>TWCK |                 | GLOC<br>OUT0 | SCIF<br>GCLK IN1 | LCDCA<br>SEG39 | CATB<br>SENSE18 |

| 46       | 46       | PA25 | 25   | VDDIO          | USBC<br>DM   | USART2<br>RXD  |                 |              |                  |                | CATB<br>SENSE19 |

| 47       | 47       | PA26 | 26   | VDDIO          | USBC<br>DP   | USART2<br>TXD  |                 |              |                  |                | CATB<br>SENSE20 |

|          | 25       | PA27 | 27   | LCDA           | SPI<br>MISO  | IISC<br>ISCK   | ABDACB<br>DAC0  | GLOC<br>IN4  | USART3<br>RTS    |                | CATB<br>SENSE0  |

|          | 26       | PA28 | 28   | LCDA           | SPI<br>MOSI  | IISC<br>ISDI   | ABDACB<br>DACN0 | GLOC<br>IN5  | USART3<br>CTS    |                | CATB<br>SENSE1  |

|          | 27       | PA29 | 29   | LCDA           | SPI<br>SCK   | IISC<br>IWS    | ABDACB<br>DAC1  | GLOC<br>IN6  | USART3<br>CLK    |                | CATB<br>SENSE2  |

|          | 30       | PA30 | 30   | LCDA           | SPI<br>NPCS0 | IISC<br>ISDO   | ABDACB<br>DACN1 | GLOC<br>IN7  | USART3<br>RXD    |                | CATB<br>SENSE3  |

|          | 31       | PA31 | 31   | LCDA           | SPI<br>NPCS1 | IISC<br>IMCK   | ABDACB<br>CLK   | GLOC<br>OUT1 | USART3<br>TXD    |                | CATB<br>DIS     |

Table 3-3.

48-pin GPIO Controller Function Multiplexing (Sheet 2 of 2)

#### 3.2.2 Peripheral Functions

Each GPIO line can be assigned to one of several peripheral functions. The following table describes how the various peripheral functions are selected. The last listed function has priority in case multiple functions are enabled on the same pin.

| Function                              | Description                               |

|---------------------------------------|-------------------------------------------|

| GPIO Controller Function multiplexing | GPIO and GPIO peripheral selection A to H |

| JTAG port connections                 | JTAG debug port                           |

| Oscillators                           | OSC0                                      |

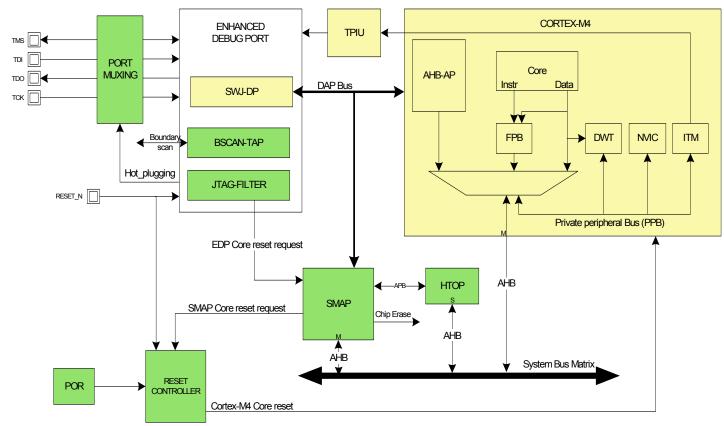

#### 3.2.3 JTAG Port Connections

If the JTAG is enabled, the JTAG will take control over a number of pins, irrespectively of the I/O Controller configuration.

|                    | JIAGFIN           | Jui            |                   |             |             |

|--------------------|-------------------|----------------|-------------------|-------------|-------------|

| 48-pin<br>Packages | 64-pin<br>QFP/QFN | 100-pin<br>QFN | 100-ball<br>VFBGA | Pin<br>Name | JTAG<br>Pin |

| 10                 | 10                | 19             | B3                | PA03        | TMS         |

| 43                 | 59                | 95             | D6                | PA23        | TDO         |

| 44                 | 60                | 96             | D10               | PA24        | TDI         |

| 9                  | 9                 | 18             | B4                | ТСК         | тск         |

Table 3-5. JTAG Pinout

#### 3.2.4 ITM Trace Connections

If the ITM trace is enabled, the ITM will take control over the pin PA23, irrespectively of the I/O Controller configuration. The Serial Wire Trace signal is available on pin PA23

#### 3.2.5 Oscillator Pinout

The oscillators are not mapped to the normal GPIO functions and their muxings are controlled by registers in the System Control Interface (SCIF) or Backup System Control Interface (BSCIF). Refer to the Section 15. "System Control Interface (SCIF)" on page 308 and Section 15. "Backup System Control Interface (BSCIF)" on page 308 for more information about this.

| 48-pin Packages | 64-pin QFN/QFP | 100-pin Packages | 100-ball VFBGA | Pin Name | Oscillator Pin |

|-----------------|----------------|------------------|----------------|----------|----------------|

| 1               | 1              | 5                | B9             | PA00     | XIN0           |

| 13              | 17             | 26               | B2             | XIN32    | XIN32          |

| 2               | 2              | 6                | B8             | PA01     | XOUT0          |

| 14              | 18             | 27               | C2             | XOUT32   | XOUT32         |

Table 3-6. Oscillator Pinout

## 3.3 Signals Description

The following table gives details on signal names classified by peripheral.

Table 3-7.

Signal Descriptions List (Sheet 1 of 4)

| Signal Name          | Function                                | Туре               | Active<br>Level | Comments |

|----------------------|-----------------------------------------|--------------------|-----------------|----------|

|                      | Audio Bitstream DA                      | C - ABDACB         |                 |          |

| CLK                  | D/A clock output                        | Output             |                 |          |

| DAC1 - DAC0          | D/A bitstream outputs                   | Output             |                 |          |

| DACN1 - DACN0        | D/A inverted bitstream outputs          | Output             |                 |          |

|                      | Analog Comparator Int                   | erface - ACIF      | FC              |          |

| ACAN1 - ACAN0        | Analog Comparator A negative references | Analog             |                 |          |

| ACAP1 - ACAP0        | Analog Comparator A positive references | Analog             |                 |          |

| ACBN1 - ACBN0        | Analog Comparator B negative references | Analog             |                 |          |

| ACBP1 - ACBP0        | Analog Comparator B positive references | Analog             |                 |          |

|                      | ADC controller interfa                  | ace - ADCIFE       |                 |          |

| AD14 - AD0           | Analog inputs                           | Analog             |                 |          |

| ADVREFP              | Positive voltage reference              | Analog             |                 |          |

| TRIGGER              | External trigger                        | Input              |                 |          |

|                      | Backup System Control I                 | nterface - BS      | SCIF            |          |

| XIN32                | 32 kHz Crystal Oscillator Input         | Analog/<br>Digital |                 |          |

| XOUT32               | 32 kHz Crystal Oscillator Output        | Analog             |                 |          |

|                      | Capacitive Touch Mod                    | ule B - CATE       | 3               |          |

| DIS                  | Capacitive discharge line               | Output             |                 |          |

| SENSE31 - SENSE0     | Capacitive sense lines                  | I/O                |                 |          |

|                      | DAC Controller                          | - DACC             |                 |          |

| DAC external trigger | DAC external trigger                    | Input              |                 |          |

| DAC voltage output   | DAC voltage output                      | Analog             |                 |          |

|                      | Enhanced Debug Port For A               | RM Products        | s - EDP         |          |

| TCK/SWCLK            | JTAG / SW Debug Clock                   | Input              |                 |          |

| TDI                  | JTAG Debug Data In                      | Input              |                 |          |

| TDO/TRACESWO         | JTAG Debug Data Out / SW Trace Out      | Output             |                 |          |

| TMS/SWDIO            | JTAG Debug Mode Select / SW Data        | I/O                |                 |          |

|                      | External Interrupt Co                   | ntroller - EIC     | ;               |          |

| EXTINT8 - EXTINT0    | External interrupts                     | Input              |                 |          |

|                      | Glue Logic Control                      | ler - GLOC         | •               |          |

| IN7 - IN0            | Lookup Tables Inputs                    | Input              |                 |          |

| OUT1 - OUT0          | Lookup Tables Outputs                   | Output             |                 |          |

| Function                             | Туре                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Active<br>Level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

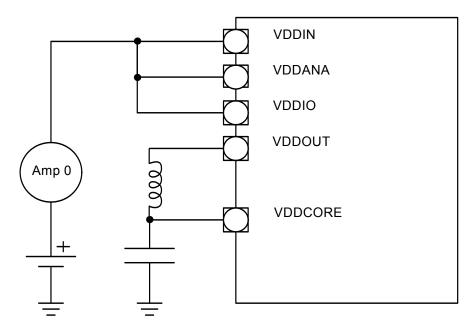

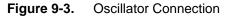

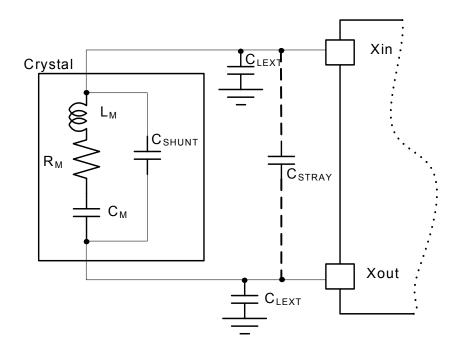

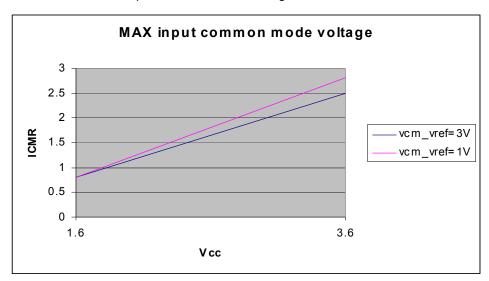

| Inter-IC Sound (I2S)                 | Controller - IIS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | С                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |